Η Diário Econômico de Taiwan ele afirma que o TSMC alcançou uma descoberta interna significativa para sua disposição final tecnologia de litografia 2 nm.

ΣDe acordo com a publicação, este marco permite à TSMC está otimista sobre uma implementação de produção inicial "Produção de Risco" 2 nm em 2023.

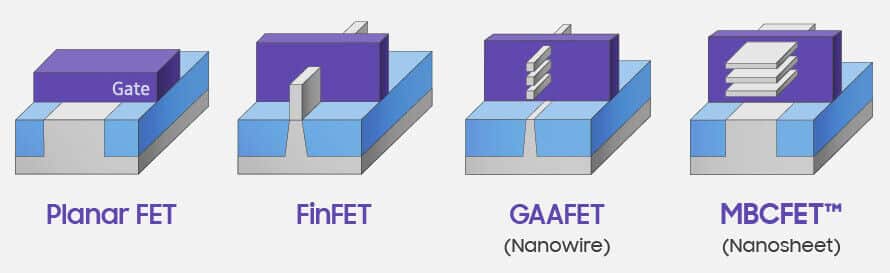

Ainda impressionantes são os relatórios que TSMC deve abandonar a tecnologia FinFet por um novo transistor de efeito de campo de canal multiponte (MBCFET) baseado na tecnologia Gate-All-Around (GAA). Esta importante descoberta está chegando um ano após a criação de uma equipe indoor pela TSMC, cujo objetivo era abrir caminho para o desenvolvimento da litografia de 2 nm.

A tecnologia MBCFET estende a arquitetura GAAFET ao pegar o transistor de efeito de campo Nanowire e "espalhá-lo" para se tornar uma Nanosheet. A ideia principal é fazer o transistor de efeito de campo XNUMXD.

Este novo transistor semicondutor de óxido de metal complementar pode melhorar o controle do circuito e reduzir o vazamento de corrente. Esta filosofia de design não é exclusiva para TSMC - Samsung planeja desenvolver uma variação deste projeto em sua tecnologia de litografia 3 nm.

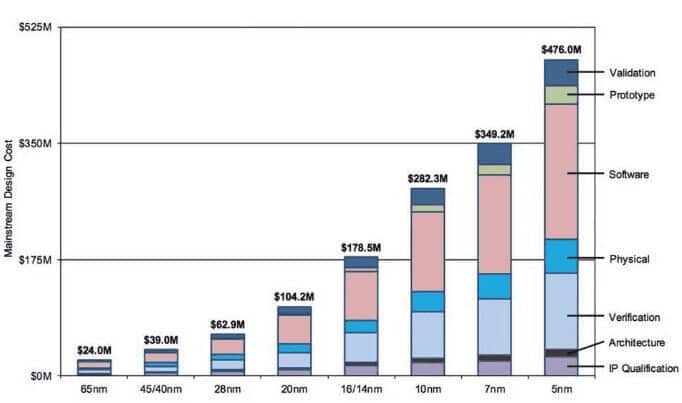

Como sempre, maior redução na escala de fabricação de chips tem um custo enorme. Em particular, o custo de desenvolvimento para a litografia de 5 nm já atingiu US $ 476 milhões, enquanto a Samsung afirma que a tecnologia GAA de 3 nm custará mais de $ 500 milhões. Claro, o desenvolvimento da litografia 2 nm, excederá esses valores ...

Não se esqueça de seguir Xiaomi-miui.gr em Google News para ser informado imediatamente sobre todos os nossos novos artigos!

Não se esqueça de seguir Xiaomi-miui.gr em Google News para ser informado imediatamente sobre todos os nossos novos artigos!